# **DIVISION CIRCUIT USING REVERSIBLE LOGIC GATES**

<sup>1</sup>Dr. John Paul Pulipati, Principal, <sup>2</sup>Rajesh Durgam, <sup>3</sup>M.Shiva Kumar, <sup>4</sup>P.Venkatapathi, <sup>5</sup>P.Anitha <sup>1</sup>principal@mrce. in,Malla Reddy College of Engineering

<sup>2</sup>Professor, Dept. of ECE, Malla Reddy College of Engineering

<sup>3</sup>Assistant Professor, Dept. of ECE, Malla Reddy College of Engineering

<sup>4</sup>Assistant Professor, Dept. of ECE, Malla Reddy College of Engineering

<sup>5</sup>Assistant Professor, Dept. of ECE, Malla Reddy College of Engineering

Abstract— In the recent years, reversible approachis becoming widely used in many domains, such as quantum computing, optical computing and ultra-low power VLSI circuit. Division has its application in the design of reversible Arithmetic Logic Unit (ALU). In this paper, we have exhibited a novel design of division sequential circuit using reversible logic gates. The proposed design of division block is based on reversible gates with reduction of garbage outputs, constant inputs, quantum cost and hardware complexity. The comparative results demonstrate that the proposed solution have less performanceand significantly better scalability than the currentdesigns

Keywords— Low power; reversible ALU; reversible gates; quantum cost; garbage outputs; hardware complexity; constant inputs; reversible division

#### **I. INTRODUCTION**

Power consumption is an essential issue in modern day VLSI (Very-Large-Scale Integration) designs. Consumption has become the essential limit of the increasing number of transistors per chip. In the recent years, many techniques have been developed at various levels in CMOS VLSI design.

At system level and algorithmic level, techniques such as use of dynamic voltage Scaling (DVS) [1] and dynamic power management (DPM), as well as alternate encoding methods.[2].

At architecture level, techniques such as

use of parallel structures, pipelining [3], the clock gating [4].

At circuit level, techniques such as use of the glitch [5].

At the technology level, techniques [6] such as VT reduction, multi-threshold voltages have beenused.

Front of these diversity methods that are dedicated to improving the power VLSI design. In this paper we have encountered the reversible logic method [7]. It has wide applications in technologies several such as the nanotechnology, low power CMOS, optical information processing, bio information and DNA computing. In 1961 Rolf Landauer [8] showed that the irreversible logic gatesor the conventional logic gates, set-to-one like AND, OR, XOR and others dissipate a certain amount of energy caused the loss for each bit information during computation (at least kTln2 for each bit of information lost, where K is the Boltzmann's constant and T is the operating temperature).

In 1973, Bennett showed that [9] in order to avoid KT\*ln2 joules of energy dissipation in a irreversible circuit, it must be built using reversible logic gates only, since there is no information loss happens in reversible circuits. In fact, division module is very important in the digital processing. Division process is one of the most difficult operations in the ALU and plays a big role in digital signal processing systems. This paper focuses on the design of division circuit sequential using reversible logic gates for positiveintegers.

## **II. BACKGROUND**

In this section, we have exhibited the essential principles definitions to reversible logic along with the analysis of quantum cost.

A. ReversibleFunctions

Reversible function can be realized by reversible logic, is a bijection. Then there is a unique one-to-one mapping between an n-input vector and a corresponding n-output vector. Avoid leading output signals of gates to more than one input

(Fan\_out).Agatewithkinputsandkoutputsiscalled k\*k

gate. An k\*k reversible logic gate can be denoted as —

, where, =(, ,..., ) is the input vector and =(, , ,..., )

..., ) is the output vector as show in fig.1 [10]. Reversible logic circuits have theoretically zero internal power dissipation because they do not lose data.

Fig.1. Reversible logic gate

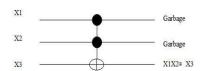

# B. Garbageoutputs

That defines the outputs of the reversible gate that is not used for further computations [11] [12]. The unutilized outputs from a gate are called "garbage output" as show infig.2.

Fig.2. Garbage output

# C. Constant inputs

Constant inputs (CIs) refer to the inputs which are used as control inputs and connected to logical '0' or '1' in order to obtain the logical function.

[13].

D. Quantum Cost

Quantum cost is the number of elementary 1\*1 like NOT and 2\*2 quantum logic gateslikeControlled

,Controlled and CNOT gates[14] [15] needed to realize the circuit.

# E. Hardwarecomplexity

This refers to the total number of the logical calculations in a circuit that is measured by counting the number of AND operations, number of NOT operations and number of EX\_OR operations [16]. To compute the hardware complexity of the reversible circuits we assume that:

a = Number of EX-OR gates. b = Number of AND gates.

6 = Number of NOT gates.

F.Synthesis of reversiblelogic

The design of reversible circuits significantly differs from the design of classical circuits. A reversible circuit should be designed using minimum number of reversible gates. One key requirement to achieve optimization is that the designed circuit must generate minimum number of garbage outputs. Equally they must use minimum number of constant inputs[17].

The fundamental rules for efficient reversible logic synthesis are:

Reduction the number of quantum cost, garbage outputs, constant inputs and hardwarecomplexity.

Avoid leading output signals of gates to more than one input (fan\_out is notpermitted).

Use a less number of reversible gates as conceivable to attain thegoal.

Various reversible gates have been previously proposed by researchers/designers till now [24-30]. Each gate has a cost associated with it called the quantum cost. The NOT gate is a 1-q-bit gates and it has a quantum cost of zero. The N-bit Controlled-Gate has quantum cost of n-1. The Feynman gate can be operates as a controlled NOT (CNOT). If A is set to '1' then the gate behaves as a Not gate, else a buffer gate. Feynman gate is widely used to surmount the fan-out problem as fan-out is not allowed in the reversible logic. It has a quantum cost of 1. The quantum cost of a Double Feynman gate is 2. The quantum cost of a Toffoli gate, TR gate and Peres gate are 4. Some examples of reversible logic gates are given by Table.1 [16-20]. These reversible gates help researchers/designers to design higher complex computing circuits. In this manuscript, we employ the reversible approach to realize a Division module.

TABLE1. Examples of some reversible logic gates

| Gate            | Quantum cost |

|-----------------|--------------|

| Feynman<br>gate | 1            |

| Not gate        | 1            |

| Tr gate         | 4            |

| Toffoli<br>gate | 5            |

| Peres<br>gate   | 4            |

| Fredkin<br>gate | 5            |

| BHA gate        | 4            |

| BHC gate        | 5            |

#### **IV. Related work**

#### A. Division operation

Essentially, the parameters of the division operation are dividend X and divisor Y as an input, and the quotient Q and remainder R as output, With X=Q\*Y+R. For division, we use shift/adder division algorithm. At every step, we Shifted the register A and X (dividend) of 1 bit to the left. If the content of the register S.A is negative, then we add the contents of register A to Y. Else we subtract the contents of register A to

Y. If the result of subtraction/addition is positive (or zero) then, the quotient bit qi = 1. Else the quotient bit qi = 0. This process is repeated ntimes.

B. Components of division circuit

• Input reversible 8 bitMUX

Figure 3 shows the 2 inputs n-bit reversible MUX where Sel

| itshe select inpu  | t, an                   | d          | aretwo                           |

|--------------------|-------------------------|------------|----------------------------------|

| inputs. If Sel = 0 | KthenK2K7               | . И\$0±1L2 | L <sub>7</sub> K <sub>7</sub> Or |

| if S =1, then      | $W_0 W_1 W_2 \dots W_n$ | V7=        | . This                           |

|                    | W. W. W.                | K          |                                  |

$$K_0 W_1 W_2 = K_0 K_1 K_2 \\ L_0 L_1 L_2 \dots \dots L_n$$

reversible MUX consists of n the applicable criteria that follow.BHA[16]gateswhichisgeneratengarbageo utputsan d needs 4n quantumcost

H BHA BHA BHA BHA BHA BHA BHA BHA U li WS 16 11 W2 WB W4 Wő Fig 3. 2-input 8-bit reversible multiplexer

Fig 3. 2-input 8-bit reversible multiplexer circuit

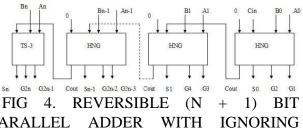

# 8+1) BIT PARALLEL ADDER/SUBTRACTOR

To perform reversible realization of (n+1) adder/subtractor circuit we may use different combinations of any of the reversible logic gates. In [20] n bit reversible adder/ Subtractor using HNG gates is presented. The carry-out of the adder/ Subtractor is ignored in the proposed division circuit. Then, the implementation of (n+1) bit parallel adder/ subtractor requires n full Adder/Subtractor units and one TS-3 gate as depicted in Fig4.

PARALLEL ADDER WITH IGNORING OUTPUTCARRY

• N BIT REVERSIBLE PIPO LEFT-SHIFTREGISTERS

In n bit PIPO shift register as show in fig.15, during every clock pulse all information bits are loaded into the register. After shift operation all information bits are transferred together to their respective outputs by the same clock pulse. In [10], an n bits reversible PIPO right- shift register has been proposed. The researchers make it compatible for implementing left-shift register. Then, the basic elements used to design left shift register are multiplexer and D-latch. Fig 5 shows the proposed left shift register.

TABLE 2. Function table for reversible PIPOshift register.

| SH | E | Finaloutput 👯                    |

|----|---|----------------------------------|

| 0  | 0 | $Q_{i-1}$ (Leftshift)            |

| 0  | 1 | $I_{i}(Parallelload)$            |

| 1  |   | <b>Q</b> <sub>i</sub> (Nochange) |

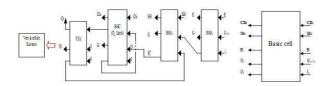

Basic cell for 1 bit reversible PIPO(Parallel Input- ParallelOutput)

#### • 3 to 1 reversibleMUX

• Basic cell for n bit reversible PIPO

Fig 5. Reversible PIPO-left-shift register

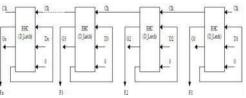

#### • n- bit reversibleregister

The reversible D-Latch is used in [16] using BHC gate. Then, in order to implement n-bits reversible register we can use n BHC gates. Fig 6 shows the n-bit reversible register. It consists of n BHC gates, produces n garbage outputs, n constant inputs and needs 5n quantum cost. The hardware complexity is 4a+6b+46.

Fig 6. (n=8)-bit reversible PIPO left shift register

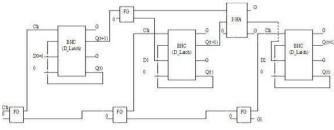

• REVERSIBLE COUNTER (MOD-8)

A mod-8 counter reversible stores an integer

value, and increments that value on each clock tick, and wraps around to 0 if the previous stored value was 7. The BHC gate [16] can be used as a D\_latch,where

So we need three flip-flops D\_ latch(BHC)where: =1

This reversible circuit produces a total number of 9 garbage outputs and 8 Constant inputs as show in Fig 7. It has a quantum cost of 28.

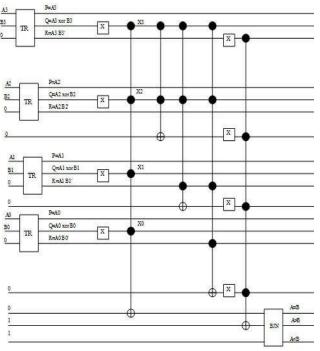

4 Bit reversiblecomparator

In this section, two 4 bit numbers are compared with each other and the result shows that if one number is superior or fewer than other or if the two numbers are equal with each other. We use NOT gate, TR gate and BJN gate [17]. For example, assume A=A3 A2 A1 A0 and B=B3 B2 B1 B0, for comparing these two numbers, we use these finite state machine as show in Fig8.

Reversible comparator is demonstrated in Fig 9. This circuit produces a total number of 10 constant inputs, 15 garbage outputs, and 18 gates. The quantum cost of this comparator is 38.

Fig 9. 4 bit reversible comparator.

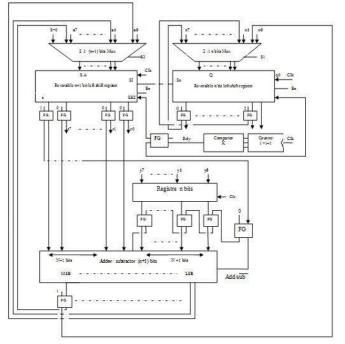

Reversible n bitdivision

The reversible components are used to implement the division operation. In this paper an optimized reversible non restoring division using reversible logic gates is presented. This circuit includes (n=8).

One n bit reversible PIPO left shiftregister

☐ One (n+1) bit reversible PIPO left shiftregister

One 2 input reversible n bitMUX

$\Box$  One 2 input reversible (n+1) bitMUX

$\Box$  One (n+1) bit reversible parallel adder/Subtractor. Algorithm:

Inputs:

S.A( ..... ) = 0 and X( ..... ) =dividend and Y( ..... )=divisor

Output s: Q( .....)=quotientand A( .....)=remainder.

Fig 10. Proposed reversible 8 bit divider circuit

Fig 10 shows the proposed reversible divider circuit. It has 2 PIPO (parallel input-parallel

output) left-shift registers. One is n+1 bits (n=8) named as S.A and other is n bits named as X. It equally contains an n bits register in order to store the

divisor. Initially  $\dots =0, X(\dots)$

= dividend, Y (  $\dots$  ) = divisor and rdy = 0. If the division process is completed then, the register X

$(\ldots)$  contains the quotient and S.A  $(\ldots)$  includes the remainder. On the other hand, when S1 = 0 then the two-input n-bit MUXselects

dividend X ( ..... ), and if S2 = 0 then the two- input(n+1)bitMUXselects S=0andA( ..... )=

0.DuringtheclockpulsewhenE=1,SH1=0andSH2 =0,

the output data from n bit MUX and (n+1)-bit MUX are

loaded into X and S.A respectively. When E = 0, both S.A and X act as left-shift registers. Initially the value of S is not important, it is important just after the left shift of S.A&X (&=Concatenated), (S.A&X means SO of register X is connected to SI of S.A). If S is high ('1') then S.A-Y is performed, else, S.A+Y is computed. The complement of the MSB (most significant bit) is loaded into q0 bit position of register X. In addition, the sum is loaded into register S.A during next clock cycle (S1= 0). It includes 2n+1 clock signals to store the quotient value into register X. Finally, after 2n+1 clock signal, X stores the quotient and A stores the

# remainder indefinitely. D. DIVISION PROCESS EXAMPLE(14/2)

| Elementary<br>operation | S.A3A2A1A0             | X3X2X1X0         |

|-------------------------|------------------------|------------------|

| loading registers       | 00000                  | 1110             |

| Shift                   | 00001                  | 110-             |

| Subtractor              | 00001<br>11101         |                  |

|                         | 1111<br>11             | 1100             |

| Shift                   | 11111                  | 100-             |

| Adder                   | <u>00010</u> 0<br>0001 | 1001             |

|                         | 00011                  | 001-             |

| Shift                   | 11101                  |                  |

| Subtrac                 | 1                      |                  |

| tor                     | 00001                  | 0011             |

| 17                      |                        |                  |

|                         | 00010                  | 011-             |

| Shift                   | 11101                  |                  |

| Subtrac                 | <u> </u>               |                  |

| tor                     | Final<br>remainder     | 0111<br>Quotient |

8þ+66.

n-bit register: number of garbage outputs = n+1, quantum cost = 5n, constant inputs = n and the hardware complexity 4a+6b+46.

n-bit left shift register: number of garbage outputs = 3n+2, quantum cost = 15n, constant inputs=3n and the hardware complexity 10a+14b+106.

(n+1)-bit left shift register: number of garbage outputs = 3n+5, quantum cost = 15n+15, constant inputs=3n+3 and the hardware complexity 20a+28b+206.

(n+1)-bit parallel adder/ subtactor: number of garbage outputs = 2n+2, quantum cost = 6n+2, constant inputs=n and the hardware complexity 7a+ 2b.

Other gates (Feynman gate): number of garbage outputs = 0, quantum cost = 3n+3, constant inputs=2n+5 and the hardware complexity 7a+2b.

#### VI. COMPARISON

In this section, we have compared the performance of the proposed design with some existing designs as depicted in table 4.

| Reversible                   | Constan t      | Quantu          | Garbag        | Hardwar     |                  | congris us u | - <b>I</b> |                |                 |

|------------------------------|----------------|-----------------|---------------|-------------|------------------|--------------|------------|----------------|-----------------|

| componen ts                  | inputs         | $\sim m \cos t$ | e             | Complexi    | t v              |              |            |                |                 |

|                              |                |                 | output        | HC(n=1)     | 5                |              |            |                |                 |

|                              |                |                 | s             |             | - TABLE          | 1            |            |                |                 |

| n bit MUX 2 :1               | 0              | 4n              | n             | 2a + 4b + 3 | 50               |              |            |                |                 |

|                              |                |                 |               | ŕ           | Compar           | ison         |            |                |                 |

| (n+1) bit MUX                | 0              | 4n+4            | n+1           | 4a + 8b + 6 | 56               |              |            |                |                 |

| 2:1                          |                |                 |               |             | Conception       | Constant     | Ouantu     | Garbag         | Hardware        |

| (n)-bit                      | n              | 5n              | n+1           | 4a + 6b + 4 |                  | inputs(n=8   | m          | e              | complexity(n=1) |

| registe                      |                |                 |               |             |                  | )            | cost(n=8)  | output         | 1 5( )          |

| r                            |                |                 |               |             |                  | ,            | )          | s              |                 |

| n-bit left shift             | 3n             | 15n             | <i>3n+2</i>   | 10a + 14b + |                  |              |            | ( <i>n</i> =8) |                 |

| register                     |                |                 |               | 6           | This work        |              |            |                |                 |

|                              |                |                 |               |             |                  | 8            | 4          | 9              | 53a + 62b +     |

| (n+1)-bit left               | 3n+3           | 15n+1           | 3n+5          | 20a+28þ+    | 20               | 8            | 4          | 9              | 436             |

| shift                        |                | 5               |               | 6           |                  | -            | 0          |                |                 |

| register                     |                |                 |               |             | <b>E</b> xisting |              | 0          |                |                 |

| (n+1)-bit                    | n              | 6n+2            | 2 <i>n</i> +2 | 7a+2b       | design           |              |            |                |                 |

| parallel                     |                |                 |               |             | in [16]          |              |            |                |                 |

| adder/                       |                |                 |               |             |                  | 8            | 4          | 1              | 65a +74 þ+52    |

| subtact                      |                |                 |               |             |                  | 9            | 5          | 0              | 6               |

| or                           |                |                 |               |             |                  |              | 4          | 3              |                 |

| Feynma<br><sup>n</sup> n-bit | 2n+5           | 3n+3            | 0             | 6 a         | Existing         |              |            |                |                 |

| <sup>n</sup> n-Dii           | reversible     | MUX: num        | ber oj ga     | rbage oui   | design           |              |            |                |                 |

|                              |                |                 |               |             | in [10]          | 9            | 5          | 1              | 59a + 67b +     |

| = n, quantur                 | $n \cos t = 4$ | n. constar      | nt inputs=    | =0 and      |                  | 1            | 3          | 0              | 336             |

| · •                          |                |                 | -             |             |                  | 1            | 8          | 6              |                 |

| he hardware o                | complexit      | y ∠a+4p+.       | 30.           |             | Existing         | 1            | 0          | 0              |                 |

|                              |                |                 |               |             | design           |              |            |                |                 |

|                              |                | V1              |               | 4           | in [13]          |              |            |                |                 |

| n+1-bitreven                 | rsibleiviU     | x:number        | orgarbag      | eoutp       | 11 [15]          | 1            | 6          | 1              | 84a + 82b +     |

$n+1\mbox{-}bitreversible MUX: number of garbage outputs$

= n+1, quantum cost = 4n+4, constant inputs=0 and the hardware complexity 4a+ 0

7

1

426

| Existing |   |   |   |             |

|----------|---|---|---|-------------|

| design   | 1 | 8 | 1 | 91a + 98b + |

| in [14]  | 6 | 4 | 8 | 506         |

|          | 1 | 6 | 1 |             |

Table 4 gives a comparison between the existing and the proposed 8 bits division designs. The proposed design reduces the garbage output, quantum cost, constant inputs as well as the hardwarecomplexity.

## VII. CONCLUSION AND FUTUREWORK

In this manuscript, we proposed one approach for designing reversible division circuits. Then we have optimized our design. We have compared this proposed design with the existing designs. The proposed module for non-restoring division has better performance in terms of constant inputs, garbage output, and quantum cost as well as the hardware complexity than that of existing designs. In the future works we will design complete reversible ALU, develop reversible hardware description language and reversible synthesis tools.

# REFERENCES

[1] Dongkun Shin, and Jihong Kim, "Intra-Task Voltage Scheduling on DVS-Enabled Hard Real-Time Systems", IEEE transactions on computer-aided design of integrated circuits and systems, VOL. 24, NO. 10, pp 1530-1549, October2005.

[2] Bishop Brock and Karthick Rajamani, "Dynamic Power Management for Embedded Systems". IEEE international SoC conference, pp 17-20, September 2003.

[9] C.H.Bernet, "Logical Reversibility of computation", IBM Journal of Research and Development, pp 525-532,1973.

[10]Noor Muhammed Nayeem, Md. Adnan Hossain, Md. Mutasimul Haque, Lafifa Jamal, Hafiz M. Hasan. Novel Reversible DivisionHardware, IEEE, pp 1134-1138. 2009

[11]Rohini H Dr. Rajashekar S Dr. PriyatamKumar. " Design of basic sequential circuits using reversible logic". IEEE, pp 2110-2115.2016

[12]Deeptha A, Drishika Muthanna, Dhrithi M, Pratiksha M, B S Kariyappa, " Design and optimization of 8 bit ALU using reversible logic", IEEE, pp 1632-1636. 20-21May.2016.

[13]Faraz Dastan1 and Majid Haghparast," A

novel nanometric fault tolerant reversible divider". International Journal of the physical Sciences Vol. 6(24), pp. 5671-5681, 16 October,2011.

[14]Faraz Dastan1 and Majid Haghparast. "A Novel Nanometric Reversible Signed Divider with Overflow Checking Capability". Research Journal of Applied Sciences, Engineering and Technology vol 4(6) pp 535-543, 2012

[15]Pallav Gupta Abhinav Agrawal, and Niraj K. Jha. " An algorithm for synthesis of reversible logic circuits" IEEE, pp 2317-2330. November 2006.

[16]A. Bolhassani and M. Haghparast, "Optimised reversible divider circuit", Int. J. Innovative Computing and Applications, pp 13-33,2016.

[17] Nagamani A, Jayashree H,H R Bhagyalakshmi, " Novel low power comparator design using reversible logic gates". IJCSE, pp 566- 574, sep 2011

[18]A. Majumder, P.L. Singh, Efficient design and analysis of N-bit reversible shift registers. Procedia Computer Science, pp 199 – 208, 2015

[19]Deeptha A, Drishika Muthanna, Dhrithi M, Pratiksha M, BS Kariyappa , "Design and optimization of 8 bit ALU using reversible logic", IEEE, pp 1632-1636. May, 21, 2016

[20]Subramanian Saravanan, Ila Vennila, Sudha Mohanram, Design and Implementation of efficient reversible arithmetic and Logic Unit. SciRes, pp 630- 642.2016.

[21]Robert Wille, Anupam Chattopadhyay, Rolf Drechsler. From Reversible Logic to Quantum Circuits: Logic Design for an Emerging Technology, IEEE, pp 268-274.2016